Apple chipmaking partner TSMC is "on track" to begin risk production of a 3-nanometer fabrication process in 2021, followed by volume production in the second half of next year, according to the foundry (via DigiTimes).

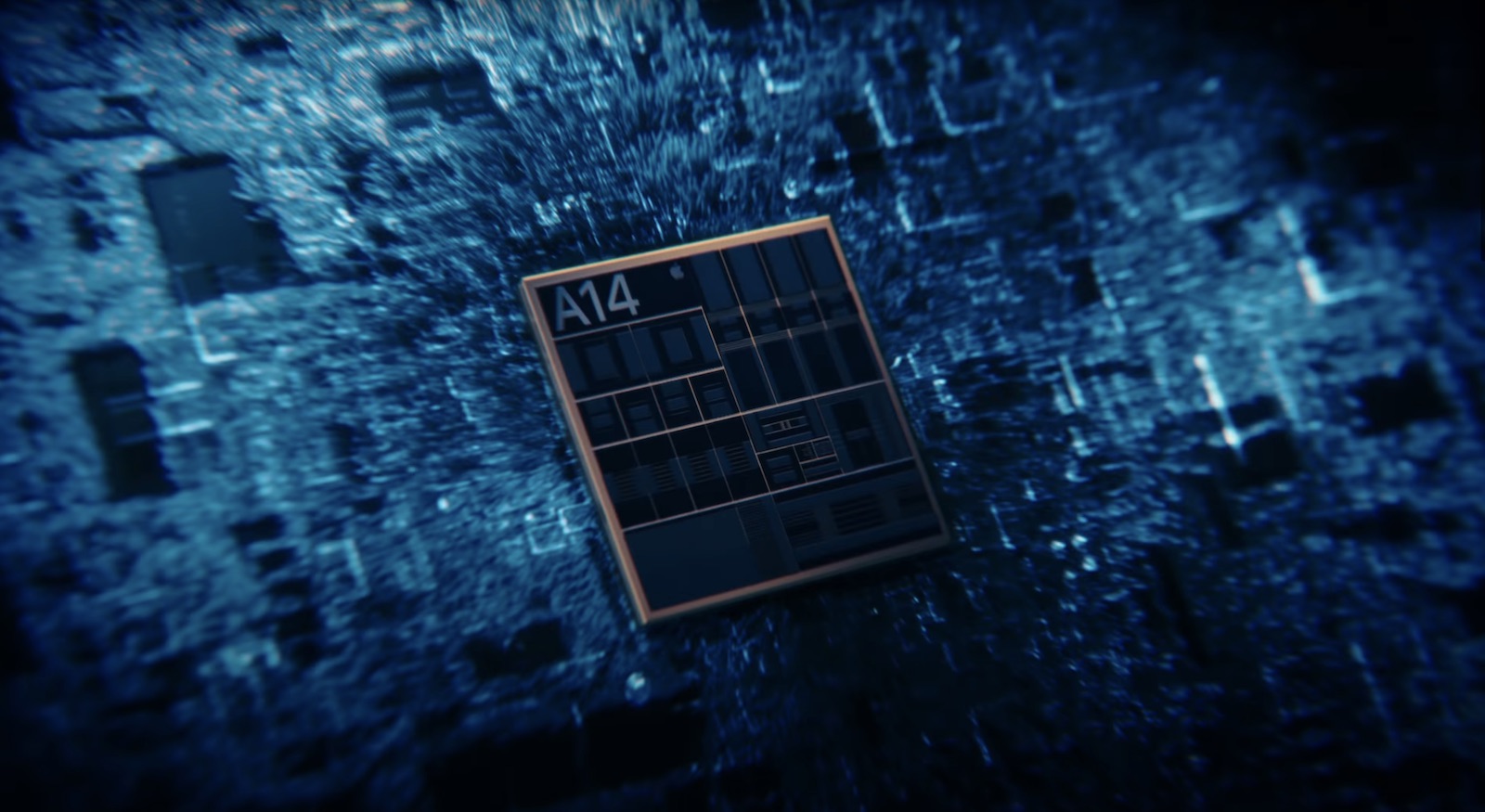

TSMC has been gradually miniaturizing its process over the years, going from a 16nm A10 chip in iPhone 7 models to a 5nm A14 chip in iPhone 12 models."Our N3 technology development is on track with good progress," said TSMC CEO CC Wei at the company's earnings conference call on January 14. "We are seeing a much higher level of customer engagement for both HPC and smartphone application at N3 as compared with N5 and N7 at a similar stage."

Apple will use a 5nm+ A15 chip for the 2021 iPhones, and TrendForce believes it is highly likely that the A16 chip in 2022 iPhones will be manufactured based on TSMC's future 4nm process, suggesting the new 3nm technology will likely be used for a potential A17 chip and potentially other future Apple silicon Macs if the company follows previous years. The 3nm process yields 30 percent and 15 percent power consumption and performance improvements over the 5nm process.

In other related news, TSMC triggered a global chip stock rally on Thursday, after outlining plans to pour as much as $28 billion into capital spending this year – more than half its projected revenue for 2021, reports Bloomberg.

TSMC's capital spending for 2021 is expected to be $25-28 billion, compared with $17.2 billion the previous year. About 80% of the outlay is said to be be devoted to advanced processor technologies. The foundry saw revenue climb 23% to $5.1 billion in the December quarter – a new record, achieved largely thanks to the success of Apple's iPhone 12 series.

TSMC also intends to build and operate an advanced semiconductor factory in Arizona, with construction planned to start in 2021 and production targeted to begin in 2024. TSMC estimates that its total spending on this project, including capital expenditure, will be approximately $12 billion from 2021 to 2029, with the facility expected to create over 1,600 high-tech professional jobs directly.

Article Link: TSMC to Begin Production of 3nm Chips This Year

Last edited: