This actually looks good and maybe this is what it looks like. Considering how proprietary its gonna be anyway, might as well than have a big old tower with no upgradability.Imagine Mac Pro Mini carrying a 3nm Apple Silicon chip. This is the cutest thing ever! 🫠

View attachment 2201633

Got a tip for us?

Let us know

Become a MacRumors Supporter for $50/year with no ads, ability to filter front page stories, and private forums.

3nm Apple Silicon: What Is It and Why Does It Matter?

- Thread starter MacRumors

- Start date

- Sort by reaction score

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

🤣👏Cue my inner George Jetson while chasing after Mac Studio when the wheel brake fails: “Jane, stop this crazy thing!”

GREAT SCOTT!!But you need 1.21 Gigawatts power it: Here is a rendering of the prototype Quantum Mac Pro from 1955

View attachment 2201639

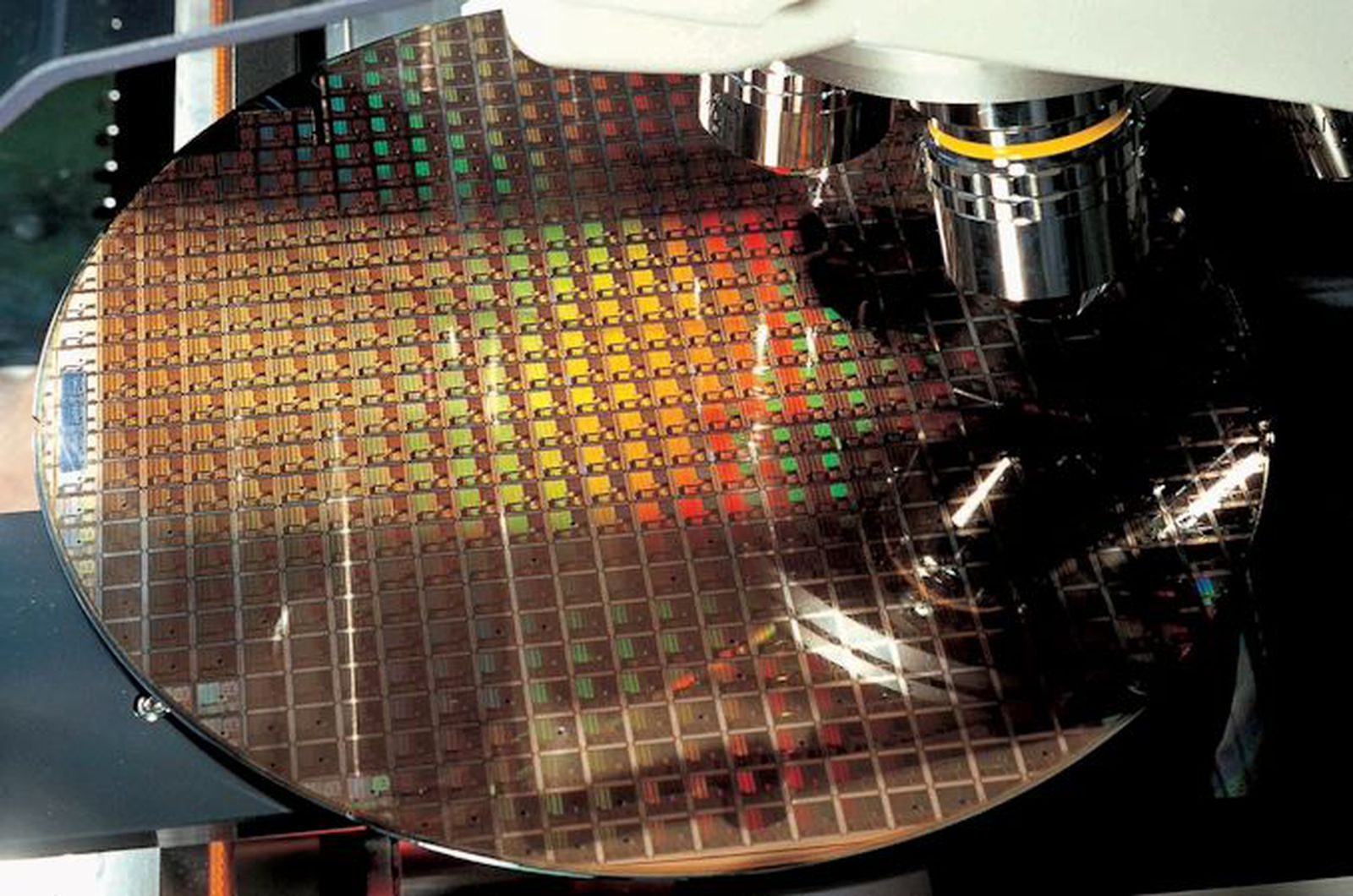

It is really sad people still believe this narrative. Companies stopped being truthful about chip sizes in the early ‘90s. A 3nm chip actually has a gate pitch of about 39nm and a metal pitch of about 26nm (differs slightly between companies). Theoretically, when both of these get to about an equal 5nm, THEN they could not get any smaller and quantum computing would ensue!0 nm = Quantum Computing

Last edited:

"3nm" seems to be some marketing BS, as you can read on Wikipedia:

That sounds like the "1 inch sensor", which has a much smaller diagonal than 1 inch.

Everyone already knows that. What matters is the difference between the previous "5nm" one and this new "3nm" one.

Why would I care? I’m a pro that doesn’t have my needs net. Where is a new Mac with more than 128GB of RAM? This can be achieved with M2 Ultra. Apple seriously mistreats their pro users. Just finish out M2 before going M3. I need the more RAM.Why would you care? Unless it is for bragging rights, it doesn’t matter. If you need the higher end Macs then you are probably using them for tasks that do a lot of multi-core processing. In that scenario, more cores trumps faster cores.

It was the 13900k that was released first. I read somewhere it would happen again with 14th gen. We didn’t have to wait for i3, months later get i5/i7 and finally months later get i9. This is what we are seeing with Apple.Errr, reportedly for Gen 15 (Meteor Lake) nope. Laptops are coming first. And the Gen 14 is a "better than they though it would be" refresh of Gen 13.

Universities are doing great work on this. A chip with transistors that no longer switch to O or 1 but instead act as a probability gate.0 nm = Quantum Computing

A structure so incredibly thin that the electricity flow is measured not in milli amps but the number of electrons that can pass through.

When they crack it they reckon the speeds achievable will render encryption useless.

Fixed that for you.M3 Pro + 30" iMac = Win!

M2 Ultras are glued together M2 Maxs, so they go into MacBook Pros.Where are 'hand me down' M2 Ultras going to go? It is too big for the chassis in the rest of the line up.

I don't think so.Typo in the article:

"TSMC is expected to begin full commercial production of 3nm chips in the fourth quarter of 2022".

I guess, they meant 2023.

Manufacturing chips is way more complicated than people think, a wafer which holds hundreds of chips could take over 1-3 months to complete due to the large amount of manufacturing steps. I wouldn't think they would start mass production on the month the next iphone is announced. Add the time needed to re-configure factories to adapt the new chip, plus testing to the mix.

Factories get paid to start making stock way earlier so it will meet demand, same goes for the rest of the tech world. If u are interested check linus's video on intel's fab tour for a small idea. Most factories run through 1, even 2 generations ahead of the market and have to create new factories for the next new technology. For example by the time the DDR4 Ram hit the market, DDR6 was already in testing stage.

Only $ 999,99 extra for these wheels? 🤣

I still see these kids fall for the “nm” which is just a marketing ploy, and roll my eyes.It is really sad people still believe this narrative. Companies stopped being truthful about chip sizes in the early ‘90s. A 3nm chip actually has a gate pitch of about 39nm and a metal pitch of about 26nm (differs slightly between companies). Theoretically, when both of these get to about an equal 5nm, THEN they could not get any smaller and quantum computing would ensue!

It’s gotten to the point that if I were at one of these semi’s marketing department, I’d get close to announcing -1nm for 2028! 🤣

Sales have collapsed for Apples high end hardware. Don’t expect any price bumps. I actually expect price cuts in Europe.It means higher prices

Apple Reportedly Agrees to TSMC Chip Price Hike After Refusing Last Week

After refusing a price hike last week from its primary chip supplier, TSMC, Apple has apparently reversed course and accepted the increase in prices set to be applied next year, according to the latest report from Economic Daily News. From January 1, 2023, TSMC plans to raise the price of 8-inch...www.macrumors.com

😂 Yeah, right.Sales have collapsed for Apples high end hardware. Don’t expect any price bumps. I actually expect price cuts in Europe.

Apple iPhones, iPads And MacBooks Are Getting More Expensive

M2 Ultras are glued together M2 Maxs, so they go into MacBook Pros.

the MBP 14/16 already got the the M2 Max . Can't possible be a "hand me down" situation when they had them first. If the Studio is going to M3 generation SoCs then the MBP probably also already left that generation.

You can spin a hand wave 'hand me down' context where perhaps the M3 Ultra comes out more than several months before the M3 Max. However, it technically isn't two just M2 max packages glued together. it is two dies that could go into a Mn Max package that are put into a different package there requirements substantially more engineering and a third die. The Mn Max dies are not glued to one another at all. They are each glued to a third die. Can say those other discarded 'Ultra Package" elements don't cost much so it is easier to throw them away. But it is being thrown away.

Additionally, the "several months before" will very likely not be a whole complete lifecycle time for a MBP. The MBP would probably need a new SoC update before the lifecycle ran out on the Mac Studio Ultra. If running concurrent that is not so much as a 'hand me down' as a co-consumer. M1 Ultra uses M1 Max dies for the most part because there was no scale for the M1 Ultra during year 1 (and most of year 2 ) of the transition. Once the whole product portfolio is built out ( M3 gen or M4 gen) there should be less of a need to bootstrap solely off laptop optimized parts.

If Apple puts Ultra on a n+2 evolution cadence then this corner case will only happen once in a while. There will be cases were sometimes the rest of line up lower down has moved on and the other haven't. Deployed as a solo Max, this also gets increasingly wafer area wasteful as go to TSMC N3 , N2 , etc. The UltraFusion connector subsystem of the die likely isn't going to shrink much. As the wafer cost up there is ZERO value add being delivered to the end user. None.

As some point the Ultra is going to need a good design chiplet; not a monolithic laptop optimized die. And vice versa. The optimized laptop die going to need to let go of the zero value-add boat anchor to complete in more competitive environments. ( or also need a good chiplet design. )

The Ultra shared over the Studio and Mac Pro should have substantively higher volume run rates than just either one of those alone.

It was the 13900k that was released first. I read somewhere it would happen again with 14th gen. We didn’t have to wait for i3, months later get i5/i7 and finally months later get i9. This is what we are seeing with Apple.

Didn't happen on Gen 11. TigerLake mobile chips first. And the Rocket Lake giant kludge came later.

The rumors is that Gen14 14900K will come first because there really won't be a mobile Gen 14. Just the desktop SoC underclocked. For high performance thin laptops there will be nothing in Gen 14. First .... only because there is nothing there. But Gen15 (MeteorLake ) will come out mobile first. there won't even be a i9 at all ( just probably later a 'hot rod' i5 ).

When the whole Intel consumer line up goes to be almost solely chiplets ... this whole i9 has to come first meme is likely going to run into problems. Which tiles/chiplets are available when it going to matter more. And the smaller ones are going to be more likely to be done (debug , fixed ) first and fab easier ( better yields on bleeding edge processes).

Just watch, Apple will release a M2 based Mac Pro and 2-3 months later M3 Mac Book Pros will come out that mop the floor of it.

I don't think anyone should buy the 1st Gen Apple Silicon Mac Pro unless it comes with M3 based hardware. And even then it still might not be as GPU powerful as the 2019 version fully decked with 2 W6800X Duos.

Apple should also release 7000 series AMD MPX cards, but they will not because then the 2019 Mac Pro will again be way faster GPU wise then whatever M variant they have coming.

There likely would no be any 7000 series card duo release (due to thermal limits and lack of Infinity Fabric). so.... it do would likely fall short of the 2 6800X Duos on broad spectrum performance ( probably some narrow FP32 small computational corner wins) . If it is 'doom' for the Apple Silicon GPU , then it should also be doom for a 7000 refresh also.

The issues is that the "two 6800X Duos" is a goofy metric to measure whether to do a new Mac Pro or not. If that was 30% of the Mac Pro user base it wouldn't be, but it likely dramatically less than that. It boils down to if the upper 20% can't get what they want then starve the lower 80% . That is just beyond goofy. The 80% are what makes it a viable product; not the 20%.

There is a sizable fraction of folks advocating for 7000 series MPX modules not to buy them , but to snarf the drivers that go with them without making substantive contributions to paying for them. It won't make sense for new MPX modules and then only relatively very small number of folks buy them .

The bulk of the MPX connector is a solution to a problem the Apple Silicon SoCs don't have ( Thunderbolt is integrated into the main package). No Infinity fabric nukes the other major non-standard connector on the module.

So have for a market for the card is a shrinking collection of systems.

Apple is damned if they do and damned if they don't. Literally the best thing they could do is release Apple Silicon Mac Pro and also updated Intel Mac Pro. Those who want to jump to Apple Silicon can do so and those who want to stay another few years on Intel + AMD can also. Win Win. (We all know this is a pipe dream though, because when has Apple ever done what was right for high end users?)

Is this really 'win/win'. The Mac Pro user base is already relatively very small. Balkanizing it into even smaller pieces isn't going to be helpful on several fronts.

1. 3rd party software vendor support. Even smaller and narrow niches of users to do high end optimiztations for. That is likely not going to return higher return on investment.... probably lower.

There is a implicit presumption here that 6000 optimized GPU stack software is exactly the same as 7000 optimized stack. Probably not true. Unless the user base on 7000 gets alot larger than the 6000 base then probably not going to get a wide variety of optimized code for this. [ It is not just a matter of Apple throwing loss leading money at it because they have a big pile in the basement to 'make it rain'. ]

2. The 'dead end' on macOS on Intel is going forward from 2023 on going to make folks look closer at long term transitions to Windows rather than have a Mac focus. Apple sinking new hardware R&D time and resources into enabling that is dubuios for the overall mac ecosystem.

If there was a card that helped the new systems just as much as the old ones that would be a Win/Win. But when it is only 1/4 or 1/6 or 1/8 of 1-2% of the systems that really isn't.

3. Even if do keep software developer optimization scheduling fragmented between AMD and Apple GPUs the time spent on AMD GPUs optimizations isn't going to help the Intel and Apple GPUs of the mac systems in still in use. The 'win' here is mainly about the needs of the few outweighs the needs of the many. Software optimized to Apple GPUs specifics of unified memory will likely work better up and down the whole product portfolio. Is the objective better software that runs on just one , on vintage/obsolete countdown clock system or the whole line up?

'win/win' is only applicable if doing both.

I am going to be a sad Mac user again if I have to build a hackintosh again and stick with Ventura until it's dead.

Doubtful that the hackintosh community is going to hold Apple back from making the transition. Nor do Mac product managers jump out bed in the morning wonder how to create a more resilient hackintoush ecosystem.

( I don't think they spend all day trying to make the hackintoush ecosystem smaller , or smallest, either.)

Is anyone besides Apple buying TSMC's first-gen N3, aka N3B?* Because if they aren't, it seems unlikely anyone but Apple will have TSMC 3 nm** products in 2023:

With N3B, there's expected to be a year delay between volume production and its appearance in products (2022 2H volume production => products expected 2H 2023). Even if we cut that in half for N3E, volume production in 2H 2023 implies we won't see products with N3E until 1H 2024.

This is the flaw here. N3B went into volume production in Dec 2022. if peg N3B a volume products in Sept 2023 that isn't a year ( 9 months) . The more pragmatic reality is that if Apple wants enough product for the September demand bubble they have to start making iPhones in June-July to met he demand. December - June 6 months.

What is stretching that to 12 months is also the size of the iPhone bubble. Not 100% the fab process. The 'bake' time for N3B is about 4 months. Add another 1-2 months for a non hyper large demand product that doesn't need to build huge inventory to cover a demand bubble and could get it out the door in 5-6. It is likely far more critical if the logistics for the rest of the system that the package with a N3E process die was going to be coupled to was finished and ready to go , than it was for SoC package.

The high number of tapeouts is the 'problem' about the presumption that 'nobody' has their system ready to go. Everybody can't be a screw up. All it would take is for one to have their system ready to go at tractable run rates.

Although TSMC said long time ago that N3E was going to start about 12 months after N3. However, that has shifted. Last year there were comments that N3E was going according to plan so well that it shifted about 1Q up. Pull a 1Q back from December and ... toward the beginning of the 2H 2023 timeframe and not the end.

Is Qualcomm going to get another very high volume SoC out the door in 2023? Probably not. Could AMD get their Zen5 dense packages out to hyperscalers for certification evaluations. Totally tractable if they have doing the work all along for last year and past tapeout a couple of months ago.

All so even more so if there is a modest wafer demand vendor sitting on N3B waiting to start in July.

*Anton Shilov of Anandtech wrote this back in Jan 2023; not sure if things have changed since then:

"Many analysts believe that the baseline N3 (also known as N3B) will be used by Apple either exclusively or almost exclusively"

[IIUC, the first variant was actually just plain N3, but it had problems and was cancelled, so the first production variant is N3B.]

Doesn't have to be N3B. If start N3E wafers through the hopper on July 15 then could have product in limited customer's shop in December. Shouldn't be a problem.

Even if Apple bought up all the N3B wafer starts that doesn't mean the N3E wafer starts have been starved to zero. If Apple is on the only one on N3B that likely means that there are just that even higher number of vendors itching to hit the 'start' button for N3E wafer starts. Any one of those vendors who started on N3B and abandoning it early in the process for N3E even more so, since likely they are behind schedule due to having to spend months 'reflowing/respinning' from N3 to N3E. The logistical train for the rest of the systems those packages were suppose to go into is likely waiting from them to catch up (or at least had time to solve any hiccups encountered in their development).

There was a report in EETimes that Apple had worked out some deal with TSMC to only pay for good dies until pretty close to Q4. ( Essentially they are not paying for the whole wafer) Folks who show up in early Q3 who are willing to pay for whole wafers and Apple is only paying for parts of a wafer ... TSMC is going to completely starve out the first customer to take more lumps from Apple? Probably not. Apple probably will get a significantly higher wafer allocation, but unlikely they are going to get it all.

If they are the only ones on N3B that is a dual edge sword. By default they get 'all' the allocation. That doesn't mean all the capacity. The downside is that they nominally would have to pull all the risk weight on the process ramp. It sounds like Apple didn't want to do that. Hence, make TSMC pay for all the bad times ( at least for now ... until TSMC does cost recovery on Apple later.). Digitimes had a 'leak' that N3 production capacity was at 45K wafer/mo, but only 50% of the capacity is being used. Makes sense for TSMC to throttle since have to eat bad dies. But also means there is capacity available. N3E isn't likely hurting for at-risk wafer starts. There is likely very low bottleneck to other folks getting their N3B or N3E design bugs worked out this Spring. The more designers that got pushed to N3E just means that the risk sharing on working the bugs out there is higher ( lower amortization costs spread over more vendors. ).

I still see these kids fall for the “nm” which is just a marketing ploy, and roll my eyes.

It’s a newer process node. That’s all that really matters.

Sales have collapsed for Apples high end hardware.

Can you produce any data for this wild assertion?

We can revist this at the end of 2023 to see what actually happened.This is the flaw here. N3B went into volume production in Dec 2022. if peg N3B a volume products in Sept 2023 that isn't a year ( 9 months) . The more pragmatic reality is that if Apple wants enough product for the September demand bubble they have to start making iPhones in June-July to met he demand. December - June 6 months.

What is stretching that to 12 months is also the size of the iPhone bubble. Not 100% the fab process. The 'bake' time for N3B is about 4 months. Add another 1-2 months for a non hyper large demand product that doesn't need to build huge inventory to cover a demand bubble and could get it out the door in 5-6. It is likely far more critical if the logistics for the rest of the system that the package with a N3E process die was going to be coupled to was finished and ready to go , than it was for SoC package.

The high number of tapeouts is the 'problem' about the presumption that 'nobody' has their system ready to go. Everybody can't be a screw up. All it would take is for one to have their system ready to go at tractable run rates.

Although TSMC said long time ago that N3E was going to start about 12 months after N3. However, that has shifted. Last year there were comments that N3E was going according to plan so well that it shifted about 1Q up. Pull a 1Q back from December and ... toward the beginning of the 2H 2023 timeframe and not the end.

Is Qualcomm going to get another very high volume SoC out the door in 2023? Probably not. Could AMD get their Zen5 dense packages out to hyperscalers for certification evaluations. Totally tractable if they have doing the work all along for last year and past tapeout a couple of months ago.

All so even more so if there is a modest wafer demand vendor sitting on N3B waiting to start in July.

Doesn't have to be N3B. If start N3E wafers through the hopper on July 15 then could have product in limited customer's shop in December. Shouldn't be a problem.

Even if Apple bought up all the N3B wafer starts that doesn't mean the N3E wafer starts have been starved to zero. If Apple is on the only one on N3B that likely means that there are just that even higher number of vendors itching to hit the 'start' button for N3E wafer starts. Any one of those vendors who started on N3B and abandoning it early in the process for N3E even more so, since likely they are behind schedule due to having to spend months 'reflowing/respinning' from N3 to N3E. The logistical train for the rest of the systems those packages were suppose to go into is likely waiting from them to catch up (or at least had time to solve any hiccups encountered in their development).

There was a report in EETimes that Apple had worked out some deal with TSMC to only pay for good dies until pretty close to Q4. ( Essentially they are not paying for the whole wafer) Folks who show up in early Q3 who are willing to pay for whole wafers and Apple is only paying for parts of a wafer ... TSMC is going to completely starve out the first customer to take more lumps from Apple? Probably not. Apple probably will get a significantly higher wafer allocation, but unlikely they are going to get it all.

If they are the only ones on N3B that is a dual edge sword. By default they get 'all' the allocation. That doesn't mean all the capacity. The downside is that they nominally would have to pull all the risk weight on the process ramp. It sounds like Apple didn't want to do that. Hence, make TSMC pay for all the bad times ( at least for now ... until TSMC does cost recovery on Apple later.). Digitimes had a 'leak' that N3 production capacity was at 45K wafer/mo, but only 50% of the capacity is being used. Makes sense for TSMC to throttle since have to eat bad dies. But also means there is capacity available. N3E isn't likely hurting for at-risk wafer starts. There is likely very low bottleneck to other folks getting their N3B or N3E design bugs worked out this Spring. The more designers that got pushed to N3E just means that the risk sharing on working the bugs out there is higher ( lower amortization costs spread over more vendors. ).

I'll believe the battery hype especially in iPhones when I actually experience it, Im a bit old fashioned and talk on my phone you know 'call people' and battery life is awful, pretty tempted by the Pixel Fold, sadly my love for Apple has diminished with its buggy OS's as in iOS 16 is buggy and still feels unfinished and Ventura wasn't bad but wasn't great either. Also it may be an amazing chip but I doubt I'll notice that in a phone, but hopefully a M3 later in the year to replace my ageing but still very functional iMac from 2017 BTO and with all the bells and whistles specced at the time would be great. Either that or I build my own windows machine and get better value for my money.

Well here is a simple question: Do 3nm chips have features that are 3/5 the size of 5 nm chips?

Register on MacRumors! This sidebar will go away, and you'll see fewer ads.