That isn't really applicable to Intel and their "efficient" cores. Their aren't really tiny and impoverished. Basically these are more space optimized broadwell (Gen 5) cores (that stop at AVX2 ) level of performance on a process shrunk node. It makes them relatively efficient. But mainly just smaller.

Apple's aren't worth much. Intel's are substantively more powerful. They are just relatively small compared to the AVX-512 and the kitchen sink large cores.

A P core can "race to sleep" pretty fast if assigned only E core level work on a mostly idling SoC. On lightweight work it isn't necessarily the "burn power like no tomorrow" option for that kind of workload.

The problem with the Intel P (performance ) cores is that they are bulky big. To match the instruction set coverage in P and E in Alder lake they just have "dead" AVX-512 dangling in there.

Intel is trying to match AMD on the core count but isn't on 7nm. So Intel largely isn't trying to shrink the E cores too small. Just small enough to make up the gap "losing" because behind on process density.

For mobile Gen 12 (Alder Lake) mobile, Intel is going to cap out the P cores at 6. ( down from desktop 8). That is in part to save space as well as power. The E cores aren't being cut. ( not as big of a space hog in addition to lower power).

That is mostly dependent upon the Windows 11 scheduler and application workload delegation.

High end Ryzen desktop Intel is competing against 16 cores. Stopping at 8 cores is a problem when it comes to trying to match in Multithread performance.

On mobile Ryzen is caps at 8 ( 16 threads ) , but Intel is more limited to 6 P. and 2C on the low end TDP mobile models) But if throw 8 "E" at the problems they should be able to pass the AMD. Just has to be about the same power the Ryzen mobile. Intel was probably also nervous about AMD maybe switching up and pushing mobile onto smaller nodes first ( instead of last ... so that could go past 8 cores ).

In short, I doubt Intel would be on this path at all if they were still 1-2 years ahead of everyone on process node fabrication skills.

Both Intel and AMD aren't throwing as much transistor budget (and bandwidth) at the iGPU as Apple is. That is another reason why Intel has a bigger budget for E cores.

On some future iterations where Intel wants to throw a substantially bigger iGPU tile/chiplet into the package then I suspect we'll see some shrinkage in E core count.

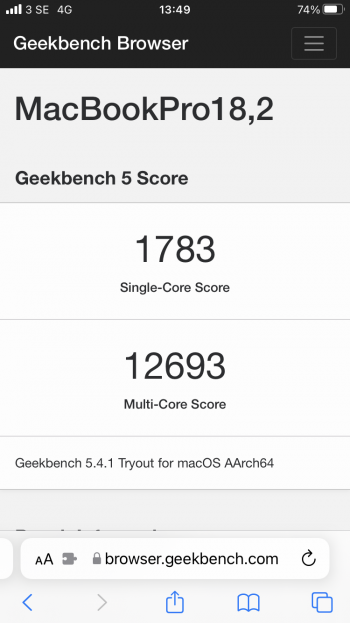

An Apple E-core is worth about 1/3 of a P core.

We do not know what a Gracemont core will be worth. We do know

- Intel claims they'll be worth substantially more than an SMT thread. That seems, uh, unlikely.

(Claim that 4x Tremont can run at 1.8x the throughput of 2 Willow Cove)

- Intel made similar unlikely claims for Tremont (worth about an SMT thread) that were demolished by the Lakefield benchmarks which showed that, rather than being worth about 60% of a large core, they were worth about 30%.

There is so much bobbing and weaving in the Intel claims (what are the cooling conditions? how much are the large and small cores being throttled by overheating?) that it's impossible to actually understand where the strengths and weaknesses are. One might have expected/hoped that the small cores would not throttle much, even when all running together, which would be a strength and boost throughput relative to the large cores. But we did not see that effect being of much value for Lakefield.

If it were any other company (AMD, ARM, QC) I'd be willing to trust and accept Intels' claims for Gracemont. But Intel have destroyed all their credibility. When we have independent benchmarks of Gracemont, then we can analyze their strategy. Until then, Intel's claims for Gracemont are as worthless as their claims for process dates have been over the past 5+ years.