Sorry for the late reply. I have spent the last year working on a quantum algorithm.

This is the experiment I have been wanting to do for a long time, but have been too lazy to try it out myself. Yes, it shows that the Mac Pro 1,1 will work with a Harpertown 5400 series processor once it has booted. Our problem must thus be in the firmware, not the hardware.

One reason for the low score might be the mismatch in the processor speeds. Your CPU was only running at 2.19 GHz. A better combination to try could be the 3 GHz X5365 and E5450.

It may be possible to run macOS in a virtual machine with only the Harpertown cores allocated.

***

Time flies and this project is not making much progress. I have thus finally decided to "upgrade" one of my two Mac Pro 1,1s with a new motherboard. I found that the Chinese Machinist MR9A Pro X99 motherboard is a perfect fit for the Mac Pro case. It provides 40 PCIe 3.0 lanes but uses only six PCIe slots instead of the standard seven of ATX motherboards. (I ordered one from AliExpress for 69€ and it arrived in under two weeks.) I will soon be taking apart my Mac Pro. This will give me a chance to study the logic board more closely and test it on a test bench.

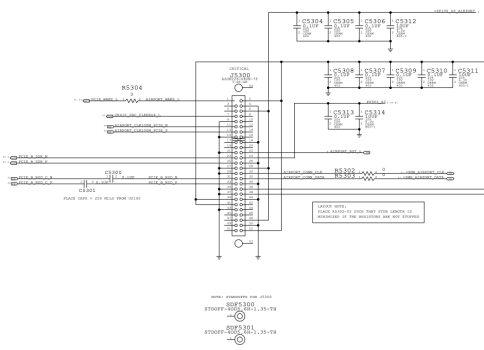

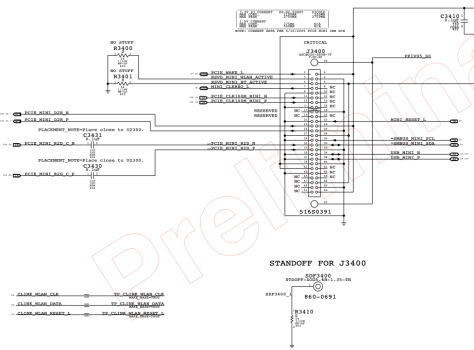

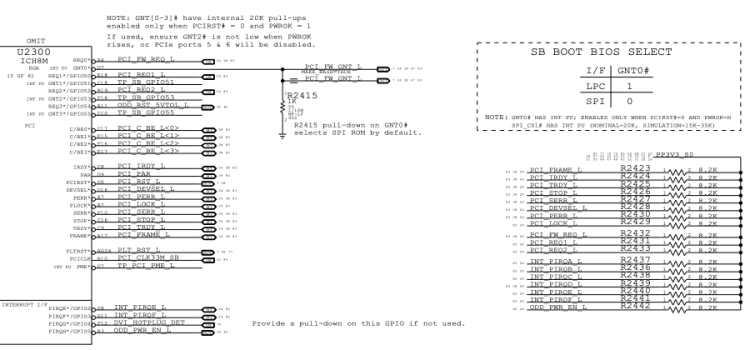

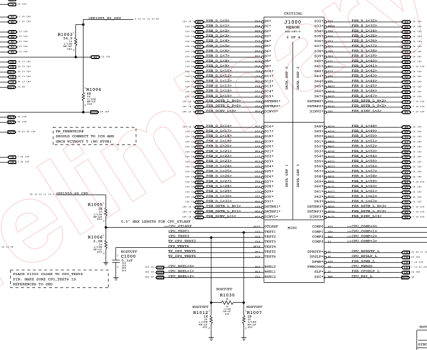

While searching for information on Intel's HD Audio interface and the Mac Pro front panel, I also made some new discoveries about the LPC bus and its connectors. I will write more in another post. I have also updated my old post on the topic from 2020.

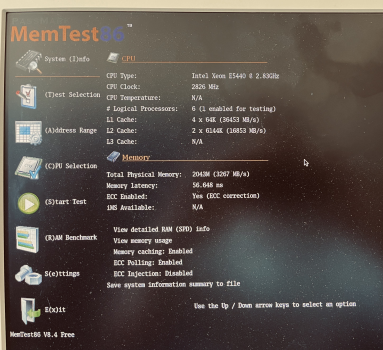

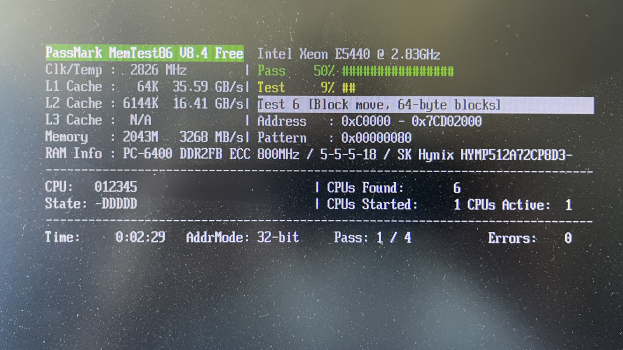

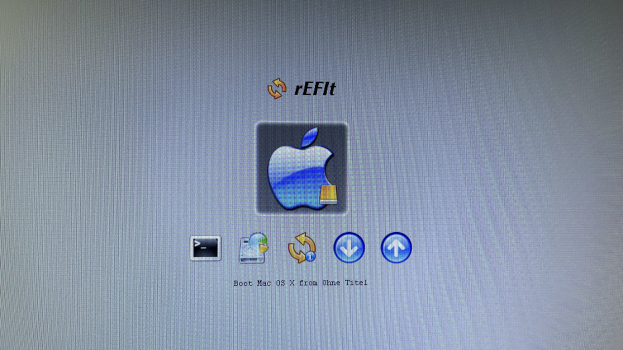

I went into more testing with mix of CPUs in the machine, it boots, but Lion crashes and I'm assuming it's because the systems sees first the E5440 and similar as when under Debian I get some time to time a "illegal instructions" message until I disable the 2 cores of the 5150.

Overall that means to me that the 5000x has no issues with managing the E5440.

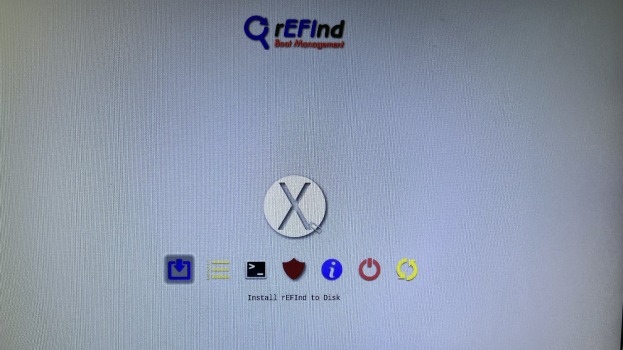

This is the experiment I have been wanting to do for a long time, but have been too lazy to try it out myself. Yes, it shows that the Mac Pro 1,1 will work with a Harpertown 5400 series processor once it has booted. Our problem must thus be in the firmware, not the hardware.

I've ran a geekbench after disabling the 5150, but results are very bad :MP1,1-E5440 geekbench5

One reason for the low score might be the mismatch in the processor speeds. Your CPU was only running at 2.19 GHz. A better combination to try could be the 3 GHz X5365 and E5450.

In addition and until a modded ROM works with the E5440, the 5150 cores have to be disabled (not sure how in the EFI Shell) before trying to boot OS X

It may be possible to run macOS in a virtual machine with only the Harpertown cores allocated.

***

Time flies and this project is not making much progress. I have thus finally decided to "upgrade" one of my two Mac Pro 1,1s with a new motherboard. I found that the Chinese Machinist MR9A Pro X99 motherboard is a perfect fit for the Mac Pro case. It provides 40 PCIe 3.0 lanes but uses only six PCIe slots instead of the standard seven of ATX motherboards. (I ordered one from AliExpress for 69€ and it arrived in under two weeks.) I will soon be taking apart my Mac Pro. This will give me a chance to study the logic board more closely and test it on a test bench.

While searching for information on Intel's HD Audio interface and the Mac Pro front panel, I also made some new discoveries about the LPC bus and its connectors. I will write more in another post. I have also updated my old post on the topic from 2020.

I ordered a POST diagnostic card from AliExpress and installed it in my Mac Pro 1,1 in the mini PCIe slot in place of the Wifi card. I was hoping it would display something during the boot process. Unfortunately the card showed nothing. It only displayed a single zero when power was turned on and stayed that way...