so the L5410 Harpertown CPU arrived today

sadly the ebay seller Messed up and sent me 1 E0 stepping L5410 rather then the 2 C0 stepping CPUs that where actually ordered...

I still pressed on with trying to get it to work in my Mac Pro 1,1/2,1 (only thing is E0 throws another variable into the system considering E0 supposedly does not even work in 3,1s let alone 1,1/2,1s)

now im going to mention a couple of things before getting to actually fitting the L5410 and that is:

I noticed that with both the Xserve1,1 and my MacPro2,1, they both lack G0 Woodcrest/Clovertown Microcode yet both of them will happily boot with G0 stepping CPUs they just run with no microcode. (Stepping 11 is G0)

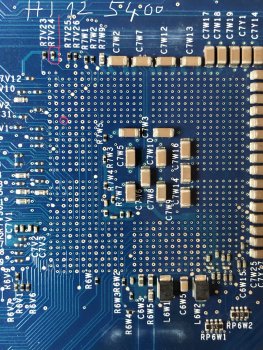

View attachment 758496

now the interesting thing is if I

add G0 microcode to the EFI on both the Xserve1,1 and the Mac Pro1,1 they will both fail to POST and light up the CPU_HLT/CPU FAIL LEDs on their respective motherboards... if I remove the microcode it boots right up.

now onto the L5410 and Harpertown CPUs.

first test was Just installing the CPU into a unmodified Mac Pro 1,1-2,1.

interestingly I had read reports that this would result in the CPU over temp LED lighting up and thats it.

but what happened is the Machine turned on it did not POST or chime but no LEDs that should not be normally lit up where lit

(the Over temp and CPU FAIL LEDs stayed off).

having confirmed that the Mac Pro as more or less expected does not work with the Harpertown CPU stock, I went about adding the E0 Harpertown Microcode (CPUID 1067A) into the Mac Pros EFI.

I then flashed it and rebooted with the X5355s to make sure I had not bricked anything Once I confirmed that I had not bricked anything I stuck the L5410 in...

moment of truth time. apply power stuff spins up ... ... CPU_FAIL LED lights up. f*ck... but interestingly this is diffrent from what the L5410s in the Mac Pro 1,1/2,1 did when there was no microcode for them in the EFI.

what im suspecting is happening is, since we deduced that the Mac Pro 2,1 will run/post with a CPU That has No microcode in the EFI. (another example of this is the iMac7,1 does not have any penryn Microcode but will work with Penryn CPUs)

I think that the Harpertown is actually trying to boot when in a stock Mac Pro 1,1/2,1 there just seems to be some sort of Hardware incompatibility stopping it from finishing POST but it does get far enough to Load Microcode if I have inserted it and fall over said microcode like the G0 CPUs do.

now the interesting thing is I vaguely remember reading a Mac Pro article where it mentioned that some people with the Intel V8 Motherboard (The Pre curser to SkullTrail) managed to hack in Harpertown Support via some Hardware mods.

sadly I cant find this article for love nor money, I would love to find out some more details on the mods they did to see if they can be Applied to the Mac Pro 1,1/2,1

it also brings back us back to what anadtech said here

https://www.anandtech.com/show/2800/upgrading-and-analyzing-apple-s-nehalem-mac-pro

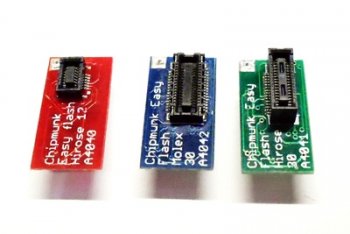

View attachment 758504

im really curious as to what those Hardware mods are (like the intel V8 board?) sadly anand works for Apple now IIRC, so I dont know if we could even contact him for details...

im also quite curious as to what a Genuine Mac Pro 2,1 Would do with harpertown CPUs since I know the Mac Pro 2,1s logic-board is slightly diffrent from the Mac Pro 1,1 Logic-board (thanks to

@Surrat s detailed analysis of a real 2,1 Lobo) Remember that I (and a lot of other people) use 1,1 boards that are flashed to 2,1 Firmware, I also still need to Test out C0 CPUs in the 1,1/2,1 but at least I have an E0 Harpertown now for testing E0 Harpertowns in a Mac Pro 3,1 if i can get ahold of a MP3,1...

I hope this all makes sense! I may or may not have been awake for over 24 hours at the time of writing this up

basically TLDR is:

Harpertowns in 1,1/2,1 are still a no go but I think its just a hardware limitation we might be able to hack round.