Or they have good marketing guys who claim this process is 3nm when it isn't.TSMC must be using some sort of alien technology to stay on ahead of everyone. /s

Now if only they can work on scaling up the production facilities to meet the growing global chip shortage.

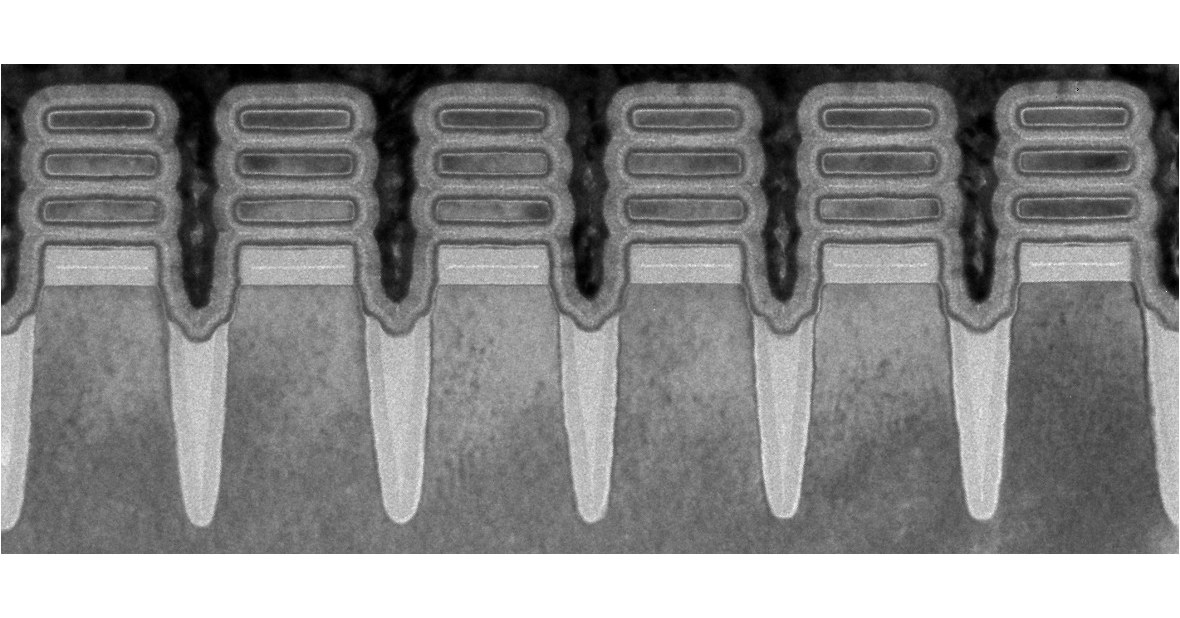

I know the Intel hate runs strong here but TSMC does not have a magical fab technology a decade ahead of Intel. They're not far off in real production capabilities. Intel's upcoming 7nm should be comparable with what TSMC calls 3nm.

Theyre just marketing terms, not actual measurements.

Last edited: